FRANKLIN TELECOMMUNICATIONS CORPORATION

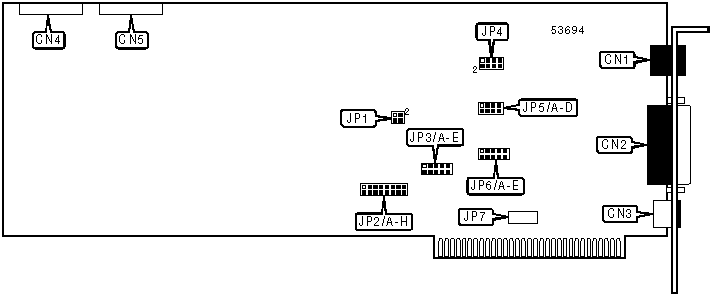

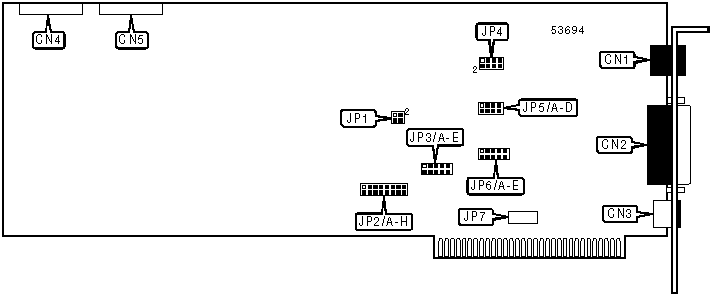

ICT-1

|

Card Type |

T1 DSU, telephony |

|

Chipset |

Unidentified |

|

I/O Options |

FABB bus, external data bus |

|

T1 Transfer Rate |

1.544Mbps |

|

T1 Protocol |

AMI, B8ZS |

|

Frame Type |

SF, ESF |

|

Data Bus |

8-bit ISA |

|

Card Size |

Full height, full length |

|

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

T1 interface via RJ-48 |

CN1 |

Franklin Above Board Bus |

CN4 |

|

T1 interface via DB-15 |

CN2 |

Franklin Above Board Bus |

CN5 |

|

External data bus |

CN3 | ||

|

SYNCHRONIZATION TYPE SELECTION | ||

|

Setting |

JP1 | |

| » |

FSYNC and C2 |

Pins 1 & 2 closed |

|

Falling edge |

Pins 3 & 4 closed | |

|

Rising edge |

Open | |

|

BASE I/O ADDRESS SELECTION | ||||||||

|

Setting |

JP2/A |

JP2/B |

JP2/C |

JP2/D |

JP2/E |

JP2/F |

JP2/G |

JP2/H |

|

000h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

|

004h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

|

008h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed |

|

00Ch |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Open |

|

010h |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed |

Closed |

|

3ECh |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

3F0h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Closed |

|

3F4h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

3F8h |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

3FCh |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

Note: A total of 256 base memory address settings are available. The jumpers are a binary representation of the decimal memory addresses. JP2/A is the Most Significant Bit and jumper JP2/H is the Least Significant Bit. The jumpers have the following decimal values: JP2/H=4, JP2/G=8, JP2/F=16, JP2/E=32, JP2/D=64, JP2/C=128, JP2/B=256, JP2/A=512. Open the jumpers and add the values of the jumpers that are open to obtain the correct memory address. (Open=1, Closed=0) | ||||||||

|

LINE BUILD OUT SELECTION | |||||

|

Setting |

JP3/A |

JP3/B |

JP3/C |

JP3/D |

JP3/E |

|

0 dB |

Closed |

Open |

Open |

Open |

Open |

|

7.5 dB |

Open |

Closed |

Open |

Open |

Closed |

|

15 dB |

Open |

Closed |

Closed |

Closed |

Open |

|

TRANSMIT/RECEIVE POLARITY CONFIGURATION | ||

|

Setting |

JP4 | |

| » |

Normal |

Pins 1 & 2, 3 & 4, 5 & 6, 7 & 8 closed |

|

Reversed |

Pins 1 & 3, 2 & 4, 5 & 7, 6 & 8 closed | |

|

T1 INTERFACE SELECTION | |||||

|

Setting |

JP5/A |

JP5/B |

JP5/C |

JP5/D | |

| » |

CN1 and CN2 |

Open |

Open |

Open |

Open |

|

CN1 only |

Closed |

Closed |

Closed |

Closed | |

|

EXTENDED SUPER FRAME FACILITY DATA LINK CONFIGURATION | ||||||

|

Setting |

JP6/A |

JP6/B |

JP6/C |

JP6/D |

JP6/E | |

| » |

ESF FDL disabled |

Open |

Open |

Open |

Open |

Open |

|

ESF FDL enabled on CN2 |

Closed |

Closed |

Closed |

Closed |

Closed | |

|

Note:For ESF FDL to be enabled, the T1 interface on CN2 must be disabled as this signal is transmitted over CN2. See the settings for jumper JP5 for more information. | ||||||

|

EXTERNAL BUS CONFIGURATION | ||

|

Setting |

JP7 | |

| » |

Disabled |

All pins open |

|

Enabled |

All pins closed | |

|

Note:The size of JP7 is unidentified. Each pair of pins vertically should be closed with a jumper so that all pins are closed. | ||