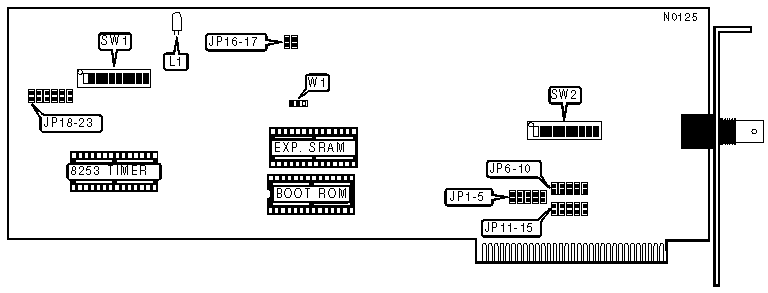

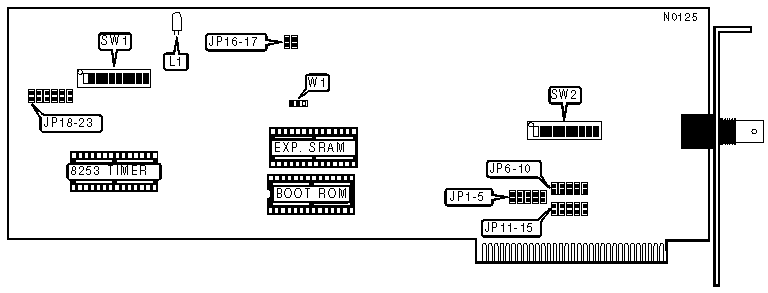

TIARA COMPUTER SYSTEMS, INC.

LanCard/A

|

NIC Type |

ARCnet |

|

Transfer Rate |

2.5Mbps |

|

Data Bus |

8-bit ISA |

|

Topology |

Star |

|

Wiring Type |

RG-62A/U 93ohm coaxial |

|

Boot ROM |

Available |

|

NODE ADDRESS |

||||||||

|

Node |

SW2/1 |

SW2/2 |

SW2/3 |

SW2/4 |

SW2/5 |

SW2/6 |

SW2/7 |

SW2/8 |

|

0 |

- |

- |

- |

- |

- |

- |

- |

- |

|

1 |

Off |

On |

On |

On |

On |

On |

On |

On |

|

2 |

On |

Off |

On |

On |

On |

On |

On |

On |

|

3 |

Off |

Off |

On |

On |

On |

On |

On |

On |

|

4 |

On |

On |

Off |

On |

On |

On |

On |

On |

|

251 |

Off |

Off |

Off |

Off |

Off |

On |

Off |

Off |

|

252 |

Off |

Off |

Off |

Off |

Off |

Off |

On |

On |

|

253 |

Off |

Off |

Off |

Off |

Off |

Off |

On |

Off |

|

254 |

Off |

Off |

Off |

Off |

Off |

Off |

Off |

On |

|

255 |

Off |

Off |

Off |

Off |

Off |

Off |

Off |

Off |

|

Note: Node address 0 is used for messaging between nodes and must not be used. A total of 255 node address settings are available. The switches are a binary representation of the decimal node addresses. Switch 1 is the Least Significant Bit and switch 8 is the Most Significant Bit. The switches have the following decimal values: switch 1=1, 2=2, 3=4, 4=8, 5=16, 6=32, 7=64, 8=128. Turn off the switches and add the values of the off switches to obtain the correct node address. (On=0, Off=1) |

||||||||

|

DIAGNOSTIC LED(S) |

||

|

LED |

Status |

Condition |

|

L1 |

On |

Data is being transmitted/received |

|

L1 |

Blinking |

Card is reconfiguring |

|

L1 |

Off |

Card is resetting or is inoperative |

|

INTERRUPT REQUEST |

|||||

|

IRQ |

JP1 |

JP2 |

JP3 |

JP4 |

JP5 |

|

2 |

Open |

Open |

Open |

Open |

Closed |

|

3 |

Open |

Open |

Open |

Closed |

Open |

|

4 |

Open |

Open |

Closed |

Open |

Open |

|

5 |

Open |

Closed |

Open |

Open |

Open |

|

7 |

Closed |

Open |

Open |

Open |

Open |

|

OPTIONAL 8253 TIMER INTERRUPT REQUEST |

||||||||||

|

IRQ |

JP6 |

JP7 |

JP8 |

JP9 |

JP10 |

JP11 |

JP12 |

JP13 |

JP14 |

JP15 |

|

2 |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Closed |

|

3 |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Closed |

Open |

|

4 |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

5 |

Open |

Closed |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

|

7 |

Closed |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

RESPONSE/RECONFIGURATION TIMEOUTS |

||||

|

Response Time |

Reconfiguration Time |

JP16 |

JP17 |

|

|

» |

74.7µs |

840µs |

Open |

Open |

|

|

283.4µs |

1680µs |

Open |

Closed |

|

|

561.8µs |

1680µs |

Closed |

Open |

|

|

1118.6µs |

1680µs |

Closed |

Closed |

|

Note: All NICs on the network must have this option set the same. |

||||

|

I/O BASE ADDRESS |

|||||||

|

Address |

SW1/1 |

SW1/2 |

SW1/3 |

SW1/4 |

SW1/5 |

SW1/6 |

|

|

» |

2E0h |

Off |

On |

Off |

Off |

Off |

On |

|

|

160h |

On |

Off |

On |

Off |

Off |

On |

|

|

1E0h |

On |

Off |

Off |

Off |

Off |

On |

|

|

260h |

Off |

On |

On |

Off |

Off |

On |

|

|

360h |

Off |

Off |

On |

Off |

Off |

On |

|

|

3E0h |

Off |

Off |

Off |

Off |

Off |

On |

|

Note: Some examples of possible settings are shown. The switches are a binary representation of the hexadecimal I/O addresses. Switch 6 is the Least Significant Bit and switch 1 is the Most Significant Bit. The switches have the following decimal values: switch 6=1h, 5=2h, 4=4h, 3=8h, 2=10h, 1=20h. Turn off the switches, add the values of the off switches, and multiply the total by 10h to obtain the correct I/O address. (On=0, Off=1) |

|||||||

|

BOOT CONFIGURATION |

||

|

Setting |

SW2/9 |

SW2/10 |

|

Boot from network, ignore bootable floppy or hard drives |

On |

On |

|

Try to boot from floppy drive A, then the network |

On |

Off |

|

Try to boot from hard drive C, then the network |

Off |

Off |

|

Try to boot from floppy drive A, then from hard drive C, then the network |

Off |

On |

|

RIM BUFFER, BOOT ROM, AND EXPANSION RAM ADDRESS CONFIGURATION |

||||

|

Address |

SW1/7 |

SW1/8 |

SW1/9 |

SW1/10 |

|

Cxxxxh |

On |

On |

Off |

Off |

|

Dxxxxh |

On |

On |

Off |

On |

|

Exxxxh |

On |

On |

On |

On |

|

Note: This table represents the first digit of three separate addresses, the rim buffer address, the boot ROM |

||||

|

BOOT ROM ADDRESS CONFIGURATION |

||||

|

Address |

JP18 |

JP19 |

JP20 |

|

|

» |

x8000h |

Open |

Closed |

Open |

|

|

Disabled |

Open |

Open |

Open |

|

|

x4000h |

Closed |

Open |

Open |

|

|

xC000h |

Open |

Open |

Closed |

|

EXPANSION SRAM CONFIGURATION |

||||

|

Size |

Address |

JP21 |

W1 |

|

|

» |

Disabled |

Disabled |

Open |

N/A |

|

|

2K x 8 (24pin) |

x4000h |

Closed |

Pins 2 & 3 closed |

|

|

8K x 8 (28pin) |

x4000h |

Closed |

PIns 1 & 2 closed |

|

Note: The manufacturer suggests the use of Hitatchi 6116 2K x 8 SRAM or Hitatchi 6264 8K x 8 SRAM chips. Most network software packages do not currently support the extra expansion memory |

||||

|

RAM BUFFER ADDRESS CONFIGURATION |

|||

|

Address |

JP22 |

JP23 |

|

|

» |

x0000h |

Open |

Closed |

|

|

x4000h |

Closed |

Open |

|

Note: The RAM Buffer cannot be disabled. |

|||