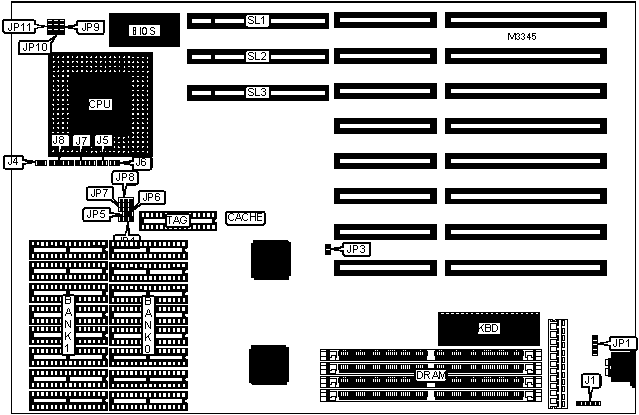

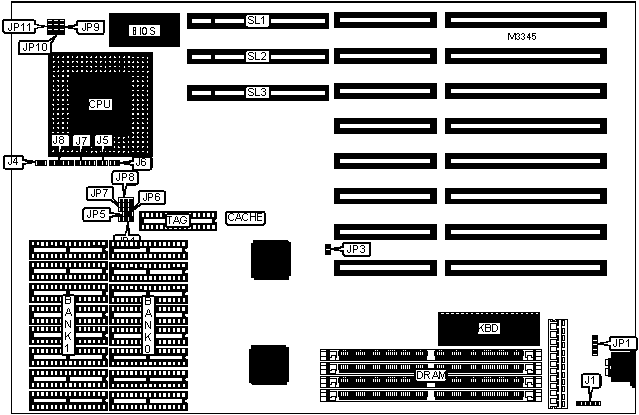

SPRINT MANUFACTURING CORPORATION

MB-P5VI

|

Processor |

Pentium |

|

Processor Speed |

60/66MHz |

|

Chip Set |

ETEQ |

|

Video Chip Set |

None |

|

Maximum Onboard Memory |

128MB |

|

Maximum Video Memory |

None |

|

Cache |

64/128/256/512/1024/2048KB |

|

BIOS |

AMI |

|

Dimensions |

330mm x 218mm |

|

I/O Options |

32-bit VESA local bus slots (3), green PC connector |

|

NPU Options |

None |

|

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

Auxiliary keyboard connector |

J1 |

Power LED & keylock |

J8 |

|

Reset switch |

J4 |

External battery |

JP1 |

|

Turbo switch |

J5 |

Green PC connector |

JP3 |

|

Turbo LED |

J6 |

32-bit VESA local bus slots |

SL1 - SL3 |

|

Speaker |

J7 | ||

|

DRAM CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

2MB |

(2) 256K x 36 |

None |

|

4MB |

(2) 512K x 36 |

None |

|

4MB |

(2) 256K x 36 |

(2) 256K x 36 |

|

8MB |

(2) 1M x 36 |

None |

|

8MB |

(2) 512K x 36 |

(2) 512K x 36 |

|

16MB |

(2) 2M x 36 |

None |

|

16MB |

(2) 1M x 36 |

(2) 1M x 36 |

|

32MB |

(2) 4M x 36 |

None |

|

32MB |

(2) 2M x 36 |

(2) 2M x 36 |

|

64MB |

(2) 8M x 36 |

None |

|

64MB |

(2) 4M x 36 |

(2) 4M x 36 |

|

128MB |

(2) 8M x 36 |

(2) 8M x 36 |

|

128MB |

(2) 16M x 36 |

None |

|

Note: The location of the banks is unidentified. Board also accepts x 32 SIMMs. | ||

|

CACHE CONFIGURATION | |||

|

Size |

Bank 0 |

Bank 1 |

TAG |

|

64KB |

(8) 8K x 8 |

None |

(1) 8K x 8 |

|

128KB |

(8) 8K x 8 |

(8) 8K x 8 |

(4) 8K x 8 |

|

256KB |

(8) 32K x 8 |

None |

(4) 8K x 8 |

|

512KB (A) |

(8) 32K x 8 |

(8) 32K x 8 |

(1) 32K x 8 |

|

512KB (B) |

(8) 64K x 8 |

None |

(1) 32K x 8 |

|

1MB (A) |

(8) 64K x 8 |

(8) 64K x 8 |

(1) 32K x 8 |

|

1MB (B) |

(8) 128K x 8 |

None |

(1) 32K x 8 |

|

2MB |

(8) 128K x 8 |

(8) 128K x 8 |

(1) 64K/128K x 8 |

|

CACHE JUMPER CONFIGURATION | |||||

|

Size |

JP4 |

JP5 |

JP6 |

JP7 |

JP8 |

|

64KB |

1 & 2 |

Open |

Open |

Open |

Open |

|

128KB |

2 & 3 |

Open |

Open |

2 & 3 |

Open |

|

256KB |

1 & 2 |

Closed |

Open |

2 & 3 |

Open |

|

512KB (A) |

2 & 3 |

Closed |

Open |

1 & 2 |

Open |

|

512KB (B) |

1 & 2 |

Closed |

Open |

1 & 2 |

Open |

|

1MB (A) |

2 & 3 |

Closed |

1 & 2 |

Open |

1 & 2 |

|

1MB (B) |

1 & 2 |

Closed |

2 & 3 |

1 & 2 |

Open |

|

2MB |

2 & 3 |

Closed |

2 & 3 |

Open |

2 & 3 |

|

Note: Pins designated should be in the closed position. | |||||

|

CPU SPEED SELECTION | |

|

Speed |

JP11 |

|

60MHz |

Pins 2 & 3 closed |

|

66MHz |

Pins 1 & 2 closed |

|

VL BUS WAIT STATE SELECTION | |

|

Setting |

JP10 |

|

0 |

Pins 1 & 2 closed |

|

1 |

Pins 2 & 3 closed |

|

VL BUS SPEED SELECTION | |

|

Setting |

JP9 |

|

<= 33MHz |

Pins 1 & 2 closed |

|

>33 MHz |

Pins 2 & 3 closed |

|

MISCELLANEOUS TECHNICAL NOTE |

|

The location of pin 1 on all jumpers is unidentified. |