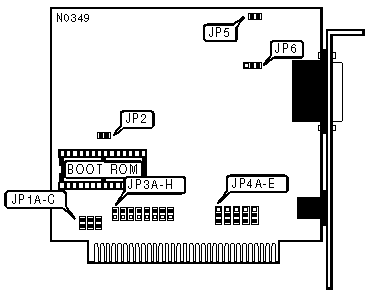

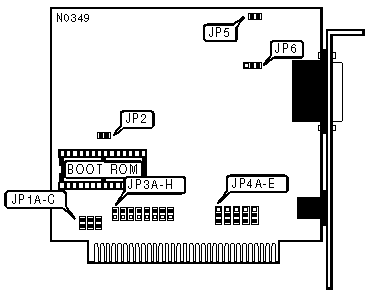

LONGSHINE MICROSYSTEM, INC.

LCS-8834T (REV. B)

|

NIC Type |

Ethernet |

|

Transfer Rate |

10Mbps |

|

Data Bus |

8-bit ISA |

|

Topology |

Star |

|

Wiring Type |

Shielded/Unshielded twisted pair AUI transceiver via DB-15 port |

|

Boot ROM |

Available |

|

I/O BASE ADDRESS | ||||

|

Address |

JP1A |

JP1B |

JP1C | |

| » |

300h |

Closed |

Closed |

Closed |

|

320h |

Closed |

Closed |

Open | |

|

340h |

Closed |

Open |

Closed | |

|

360h |

Closed |

Open |

Open | |

|

380h |

Open |

Closed |

Closed | |

|

3A0h |

Open |

Closed |

Open | |

|

3C0h |

Open |

Open |

Closed | |

|

3E0h |

Open |

Open |

Open | |

|

BOOT ROM | ||

|

Setting |

JP2 | |

| » |

Disabled |

Open |

|

Enabled |

Closed | |

|

INTERUPT REQUEST | |||||

|

IRQ |

JP3A |

JP3B |

JP3C |

JP3D | |

|

2/9 |

Closed |

Open |

Open |

Open | |

| » |

3 |

Open |

Closed |

Open |

Open |

|

4 |

Open |

Open |

Closed |

Open | |

|

5 |

Open |

Open |

Open |

Closed | |

|

DMA CHANNEL | |||||

|

Channel |

JP3E |

JP3F |

JP3G |

JP3H | |

| » |

Disabled |

JP3E/pin 1 connected to JP3F/pin 1 and JP3G/pin 1 connected to JP3H/pin 1 | |||

|

DMA1 |

Closed |

Open |

Closed |

Open | |

|

DMA3 |

Closed |

Open |

Open |

Closed | |

|

BASE MEMORY ADDRESS | ||||||

|

Address |

JP4A |

JP4B |

JP4C |

JP4D |

JP4E | |

|

C000h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

C200h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

C400h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

C600h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 | |

| » |

C800h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

|

CA00h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

CC00h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

CE00h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 | |

|

D000h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

D200h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

D400h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

D600h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

D800h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

DA00h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

DC00h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

DE00h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 | |

|

E000h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

E200h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

E400h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

E600h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

E800h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

EA00h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

EC00h |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

EE00h |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 | |

|

F000h |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 | |

|

F200h |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 | |

|

Note:Pins designated should be in the closed position. | ||||||

|

CABLE TYPE | ||

|

Type |

JP5 | |

| » |

Shielded/Unshielded twisted pair |

Closed |

|

AUI transceiver via DB-15 port |

Open | |

|

LINK INTEGRITY TEST | ||

|

Setting |

JP6 | |

| » |

Enabled |

Pins 2 & 3 closed |

|

Disabled |

Pins 1 & 2 closed | |

|

Note:Link integrity testing is only operational when the cable type is shielded/unshielded twisted pair. | ||